HoustonMicro

TM

"... Over 30 years in space systems design, ground testing, integration, and embedded electronics design / manufacturing..."

HoustonMicro Computer Company, LLC. 16821 Buccaneer Ln. Suite 106. Houston, Tx. 77058

- Fully Customizable

- Test Data Generation

- FPGA & ARM/CPU Data Processing

- Proof-of-Concept Prototyping

- User Definable. User Programmable.

- General Purpose Laboratory Instrument

R/T BERD

Real-Time, Closed-Loop Bit Error Rate Tester (BERT)

- Closed-Loop "Any Data" Bit Error Rate Tester

- Not Limited to Repeating or PRBS Patterns

- Real-Time "in the loop" Data capable

- TTL, PECL, RS422, or LVDS Inputs

(user specified)

- 50 MHz and 150 MHz Units Available

- Ideal for Space Systems and Telemetry Testing

(Click Image for More Information)

(Click Image for More Information)

- Alternative FPGA/CPU Processor Boards

- Integration of COTS and/or Custom Designs

- Alternative I/O Interfaces/Connectors

- In-House Board Design

- Customized Chassis Color and Sizing

- Customer Specified Panel Silk-Screening

- Project and Systems Integration

Custom System Design & Integration

Signal Transport / Transceivers

Transmit, Condition, Translate Signals

for Communications at Long Distance

- Condition Signals for longer haul communications

- Differential or Optical Transmission

- Reproduce - or Translate Signals - at End Receiver

- TTL, LVTTL, RS422, PECL, LVDS Capable

- Interfaces Directly with our FPGA Platforms

- Or use as standalone Signal Conditioners/Translators

(Click Image for More Information)

(Click Image for More Information)

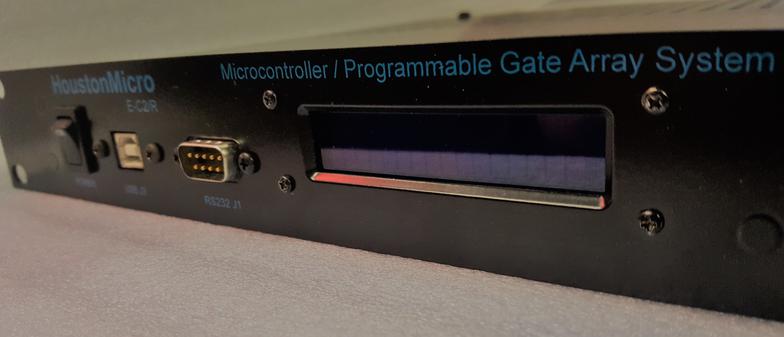

User Definable Laboratory Instruments

FPGA-ARM Programmable Systems

Avionics - Telemetry - Ground Testing - Embedded Electronics - Systems Integration

...................................................................................................................................................................................................................................................

...................................................................................................................................................................................................................................................

...................................................................................................................................................................................................................................................

...................................................................................................................................................................................................................................................